- [12] L.-W. Li, P.-S. Kooi, M.-S. Leong, T.-S. Yeo, and S.-L. Ho, "Input impedance of a probe-excited semi-infinite rectangular waveguide with arbitrary multilayered loads: Part I—Dyadic Green's functions," *IEEE Trans. Microwave Theory Tech.*, vol. 43, no. 7, pp. 1559–1566, July 1995.

- [13] —, "Input impedance of a probe-excited semi-infinite rectangular waveguide with arbitrary multilayered loads: Part II—A full-wave analysis," *IEEE Trans. Microwave Theory Tech.*, vol. 45, no. 3, pp. 321–329, Mar. 1997.

- [14] J. Liang, H. Chang, and K. A. Zaki, "Coaxial probe modeling in waveguide and cavities," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 2172–2180, Dec. 1992.

- [15] M. Saad, "A more accurate analysis and design of coaxial-to-rectangular waveguide end launcher," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 129–134, Feb. 1990.

- [16] A. Alvarez and M. Guglielmi, "New simple procedure for the computation of the multimode admittance matrix of arbitrary waveguide junctions," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Orlando, FL, May 1995, pp. 1415–1418.

- [17] R. E. Collin, *Foundations for Microwave Engineering*, 2nd ed. New York: McGraw-Hill, 1992.

- [18] G. Conciauro, M. Bressan, and C. Zuffada, "Waveguide modes via an integral equation leading to a linear matrix eigenvalue problem," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 1495–1504, Nov. 1984.

- [19] P. Arcioni, M. Bressan, G. Conciauro, and L. Perregini, "Wide-band modeling of arbitrarily shaped *E*-plane waveguide components by the boundary integral-resonant mode expansion method," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 2083–2092, Nov. 1996.

- [20] P. Arcioni, M. Bressan, and G. Conciauro, "Wide-band analysis of planar waveguide circuits," *Alta Freq.*, vol. LVII-N.5, pp. 217–226, June 1988.

- [21] P. Arcioni, "Fast evaluation of modal coupling coefficients of waveguide step discontinuities," *IEEE Microwave Guided Wave Lett.*, vol. 6, pp. 232–234, June 1996.

- [22] V. E. Boria, G. Gerini, and M. Guglielmi, "An efficient inversion technique for banded linear systems," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1997, pp. 1567–1570.

- [23] M. Guglielmi, "Simple CAD procedure for microwave filter and multiplexers," *IEEE Trans. Microwave Theory Tech.*, vol. 42, no. 7, pp. 1347–1352, July 1994.

## Single-Ended HEMT Multiplier Design Using Reflector Networks

Donald G. Thomas, Jr. and G. R. Branner

**Abstract**—Microwave and RF frequency multipliers are employed in a large number of communications, radar, civilian, and military systems. This paper presents the development of active doublers operating in *S* and *C* frequency bands. These devices are unique in that high electron-mobility transistors (Fujitsu FHX35LG) are employed in an unbalanced configuration utilizing "reflector" networks simultaneously on the input and output to reflect the second harmonic signal into the gate of the device and the fundamental signal into the drain simultaneously at appropriate phase angles to optimize performance. Measured and simulated results are presented on over 20 multiplier designs to verify the design philosophy. Conversion gains of approximately 7 dB are presented for narrow-band designs (5% bandwidth), 5 dB for medium-bandwidth designs (15%), and 4 dB for wide-bandwidth designs (35%). The fundamental and third harmonic rejection is approximately 40 dBc for the narrow-band designs and greater than 50 dBc for the medium and wide-band designs.

### I. INTRODUCTION

Numerous techniques exist for realization of frequency multipliers using passive or active devices. While high electron-mobility transistors (HEMTs) are traditionally employed in high-gain or low-noise amplifiers, less information is available on their use in multiplier applications. This is in marked contrast with multiplier realizations employing bipolar and FET devices.

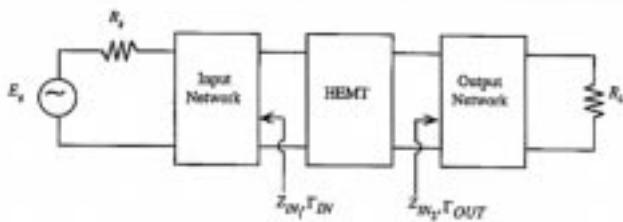

The basic configuration of Fig. 1 is employed in the frequency multiplier realization of this paper. The input network is designed to pass the fundamental frequency component to the gate of the HEMT (common-source configuration), while suppressing higher harmonic components. Likewise, the output network suppresses the fundamental and other undesired harmonics, while passing the desired harmonic. The frequency multiplier reflector network design philosophy implemented in this paper is applied to frequency doublers utilizing a fundamental frequency of 3 GHz as a vehicle.

As mentioned previously, a primary objective of the output and input networks is to suppress the fundamental and second harmonics, respectively. In the process of suppressing the undesired signals, it appears that not a great amount of attention has been focused on the concept of reflecting signals back into the device from the input and output networks, although it has been utilized occasionally as pointed out below. The device nonlinearities cause harmonics and the fundamental to mix with other frequency components and either enhance or degrade the signal at the desired output harmonic. Therefore, it is important for the reflected signal to be phased properly to interfere constructively with the desired harmonic. Thus, in concert with their primary filtering and matching functions, the input and output networks of Fig. 1 can be designed in such a way that they are reflector networks meeting the above criteria.

Due to the complexity of calculating the actual effects of the reflector networks, the published literature to date on this topic is sparse [1]–[4]. Using reflector networks as a design tool for frequency doublers, Hirota [1] gave simulated data on the effects of a reflector network on the output of a GaAsFET versus conversion gain, and realized

Manuscript received November 24, 1998; revised September 18, 2000.

D. G. Thomas, Jr. is with Panasonic—MCUSA, Peachtree City, GA 30269 USA (e-mail: thomasd@Panasonic-mcusa.com).

G. R. Branner is with the Department of Electrical and Computer Engineering, University of California at Davis, Davis, CA 95616 USA.

Publisher Item Identifier S 0018-9480(01)03317-8.

Fig. 1. Network configuration model.

a narrow-band conversion gain of 2.9 dB. Borg [2] and Rauscher [3] showed that there is an advantage in using a reflector circuit on the output. Rauscher<sup>1</sup> primarily used simulated data without experimental data to verify the accuracy of the computer simulations. In the final multiplier design, the multiplier possessed less than 0 dB of conversion gain after requiring tuning. Based on an examination of the literature, there does not appear to be a significant amount of multiplier design incorporating reflector networks, especially on both input and output ports simultaneously. Additionally, very little, if any, reflector-based work provides both highly accurate modeled and measured data.

The multiplier realizations presented in this paper are unique in that the analysis quantitatively assesses the effect of reflector networks on both input and output ports simultaneously and is performed on HEMT<sup>2</sup> transistors. Measured and modeled data are presented throughout the analytical process to validate the results. A number of designs are presented, which produce high conversion gains, narrow, medium, and wide bandwidths, and operate with low dc power consumption due to HEMT biasing at pinchoff ( $V_{gs} = V_p$ ). Furthermore, in contrast with previous results, alternate designs for reflector networks for HEMT multipliers are also discussed, employed, and experimentally verified.

## II. ANALYSIS OF REFLECTOR NETWORK EFFECTS CONSIDERATION OF REFLECTION PHASE ANGLE

As mentioned above, for optimization of conversion gain, the input and output networks depicted in Fig. 1 are designed such that they are reflector networks in addition to their primary functions of filtering and matching. These reflector networks are utilized below in the synthesis of frequency doublers operating at a fundamental frequency of 3 GHz. As alluded to previously, the input network of Fig. 1 should be designed such that it reflects the second harmonic component back into the gate at the proper phase angle to interfere constructively for optimum conversion gain. Similarly, the output network is designed such that it reflects the fundamental signal properly phased into the drain of the HEMT.

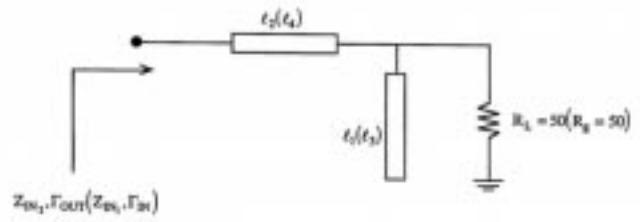

Fig. 2 shows a fundamental reflector network topology, which may be employed for output and input networks (Fig. 1). In results presented below,  $\ell_1$ ,  $\ell_2$ ,  $Z_{IN2}$ ,  $\Gamma_{OUT}$ , and  $R_L$  are employed to describe the output reflector network, while the parameters in parenthesis ( $\ell_3$ ,  $\ell_4$ ,  $Z_{IN1}$ ,  $\Gamma_{IN}$ , and  $R_g$ ) describe the input reflector network as viewed from the gate. That these networks do, in fact, provide the requisite reflection at  $f_o$  and  $2f_o$  for output and input can be seen from computation of  $\Gamma_{OUT}$  and  $\Gamma_{IN}$ , respectively, as  $\ell_2$  and  $\ell_4$  are varied over the ranges of interest.

In concert with the aforementioned objectives, with  $\lambda_{f_o}$  equal to the wavelength at the fundamental frequency,  $\ell_1$  equals a

Fig. 2. Fundamental output (input) reflector network.

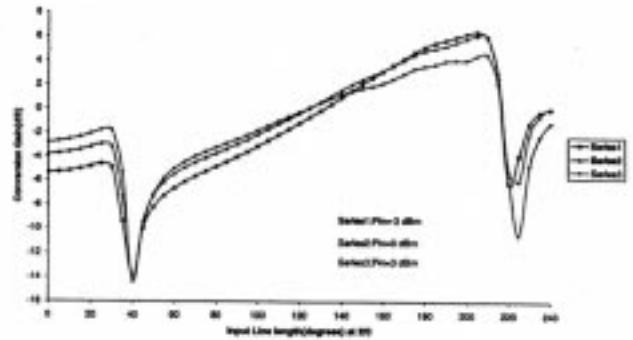

Fig. 3. Simulated conversion gain of frequency doubler versus input transmission line length ( $\ell_4$ ) at the second harmonic ( $V_{gs} = -0.6$  V,  $V_{cls} = 3$  V).

quarter-wavelength ( $\ell_1 = \lambda_{f_o}/4$ ) and  $\ell_2$  is nominally a half-wavelength ( $\ell_2 = \lambda_{f_o}/2$ ) at the fundamental frequency ( $f_o$ ) for the output reflector network. Similarly, with  $\lambda_{2f_o}$  equal to the wavelength at the second harmonic,  $\ell_3$  and  $\ell_4$  are a quarter-wavelength ( $\ell_3 = \lambda_{2f_o}/4$ ) and nominally a half-wavelength ( $\ell_4 = \lambda_{2f_o}/2$ ), respectively, at  $2f_o$ .

### A. Effect of Reflection Phase Angle on Conversion Gain

Although more exotic reflector networks will be subsequently introduced, initial observations are developed utilizing the circuits depicted in Fig. 2. Initially, optimum narrow-band conversion gains will be illustrated by optimizing the phase angles of  $\Gamma_{IN}$  and  $\Gamma_{OUT}$  via  $\ell_4$  and  $\ell_2$ , respectively. The HEMT employed is the Fujitsu FHX 35 LG and its computer model can be obtained from [5]. Furthermore, comparisons between the computer model and measured device data can be observed in [6, Fig. 2].

With the parameters of the fundamental output network constrained to the aforementioned nominal values, Fig. 3<sup>3</sup> shows the effect of varying  $\ell_4$  of the fundamental input reflector network over a range from 0° to 240° (at  $2f_o$ ) for three different input powers (-3, 0, and +3 dBm). These results quantitatively illustrate the effect of stub location on conversion gain for second harmonic energy reflection at the gate.

The maximum conversion gain is seen to occur at  $\ell_4 \approx 200^\circ$  at  $2f_o$ , and it may also be observed that the conversion gain variation may be as great as 20 dB over this range of  $\ell_4$ . Fig. 4 presents analogous data for variation of  $\ell_2$  (fundamental output reflector network) from 0 to  $\lambda_{f_o}/2$  (180° at  $f_o$ ),  $\ell_1 = \lambda_{f_o}/4$  while simultaneously utilizing the nominal input reflector network  $\ell_3 = \lambda_{2f_o}/4$ ,  $\ell_4 = \lambda_{2f_o}/2$ . These results demonstrate that there is as much as a 27-dB variation in

<sup>1</sup>Also provides analysis data for an input reflector.

<sup>2</sup>The Fujitsu FHX 35 LG HEMT transistor is employed in this paper. Its computer model can be accessed from the HP EESOF LIBRA Device Model Library [5], [6, Fig. 2].

<sup>3</sup>All results in the remaining figures have the HEMT biased with  $V_{gs} = -0.6$  V,  $V_{cls} = 3$  V and  $P_{IN} = 0$  dBm unless otherwise specified.

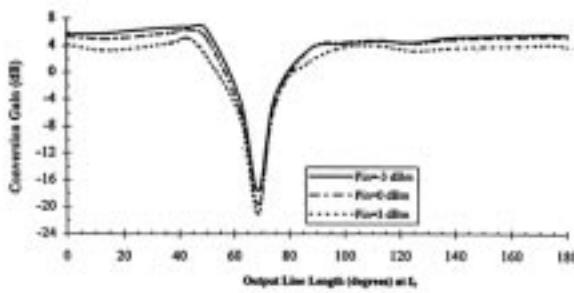

Fig. 4. Simulated conversion gain of frequency doubler versus output transmission line length ( $\ell_2$ ) at  $f_o(V_{gs} = -0.6$  V,  $V_{ds} = 3$  V).

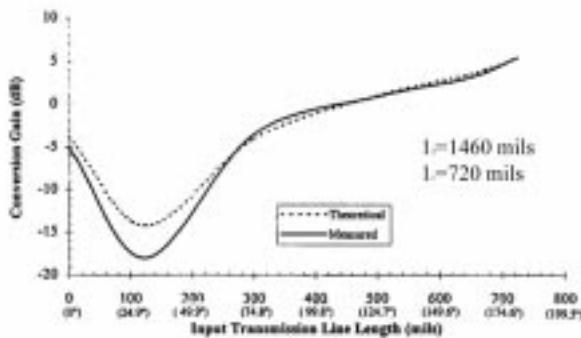

Fig. 6. Conversion gain of HEMT doubler versus output transmission-line length ( $\ell_2$ ) at  $f_o(P_{in} = 0$  dBm,  $V_{gs} = -0.6$  V,  $V_{ds} = 3$  V).

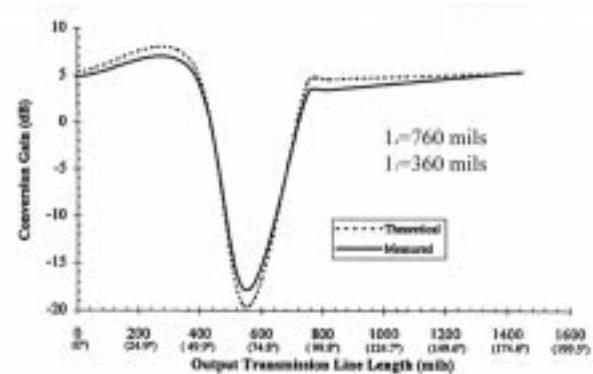

Fig. 5. Conversion gain of HEMT doubler versus input transmission line length ( $\ell_4$ ) at  $2f_o(P_{in} = 0$  dBm,  $V_{gs} = -0.6$  V,  $V_{ds} = 3$  V).

conversion gain and that the optimal length for  $\ell_2$  is  $\approx 44^\circ$  to realize maximum conversion gain.

The efficacy of the previous models in generating accurate results has been authenticated by the development of in-depth experimental data. Toward this end, a series of 16 distinct multipliers were designed, constructed, and tested. The passive circuits utilized sections of  $50\Omega$  line realized in 20-mil Duroid, copper thickness 1.5 mil, linewidths realized measured at  $\approx 60$  mil,  $\epsilon_r \approx 2.17$ .

The first series of experimental designs (eight distinct circuits of varying values of  $\ell_4$ ) authenticated the predicted results of Fig. 3 for the input reflector network. The comparative results are presented in Fig. 5 as conversion gain versus  $\ell_4$ . The responses are seen to agree exceptionally well for lengths beyond  $50^\circ$  ( $\Delta \leq 2$  dB), and for values below  $50^\circ$ , they follow the response trend with a worst-case difference of 5 dB. *Realized* dimensions are presented in Figs. 5 and 6.

The second series repeated the above experimental process duplicating the conditions of Fig. 4 ( $0 \leq \ell_2 \leq \lambda_{f_o}/2$ ) with eight distinct output networks. Simulated and measured results compare very favorably over the entire range of  $\ell_2$  values (Fig. 6). These results (Figs. 5 and 6) provide the following two significant conclusions: 1) measured and modeled results agree quite closely, and this provides confidence in predictive conclusions in the ensuing HEMT-based designs and 2) requisite line lengths and reflection angles providing optimum conversion gains can easily be extracted from the data.

### III. CIRCUIT DESIGN

#### A. Narrow-Band Doubler Design

Synthesis of a narrow-band HEMT doubler utilizes the fundamental input and output reflector networks (Fig. 2) as a basis in conjunction

Fig. 7. Narrow-band HEMT doubler design.

with the results of Figs. 3 and 5. A simulation of this circuit topology provides a prediction of a center-band conversion gain of  $\approx 7$  dB, given the respective electrical lengths of  $\ell_4$  and  $\ell_2$  of  $180^\circ$  at  $f_o$  and  $2f_o$ , respectively.

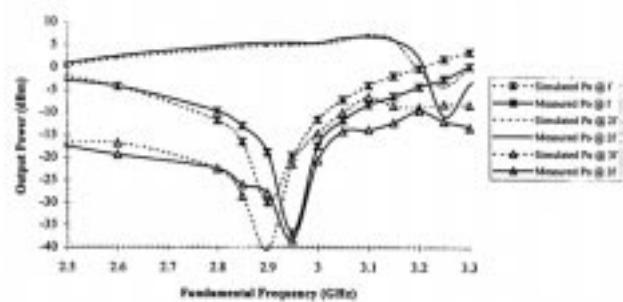

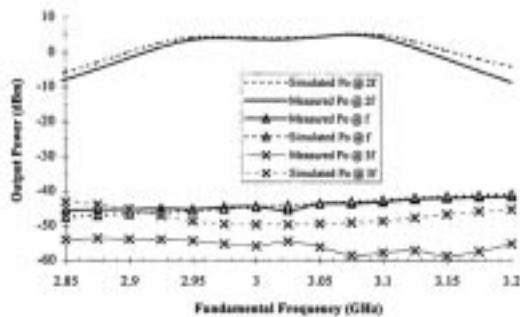

The measured and simulated performance of this multiplier realization are presented in Fig. 7. A perusal of this figure reveals that the measured conversion gain is  $\approx 6$  dB, that fundamental and third order suppression are greater than 40 dBc at a fundamental frequency of 2.95 GHz, and that measured and simulated results are in agreement. The narrow-band response (typically 5%–10%) of this design is an outcome of the application of single stub input and output reflector realizations.

An alternative narrow-band design creates more rolloff of the conversion gain response by synthesizing an output reflector network consisting of a length of transmission line cascaded with a bandpass filter structure. In this realization, the length of the cascaded transmission line is adjusted to provide the proper output reflector network phase angle for optimum conversion gain ( $\approx 44^\circ$  and a corresponding theoretical coefficient angle of  $\approx 93^\circ$  at the fundamental frequency, as shown in Figs. 4 and 6). This presents the correct impedance to resonate the drain reactance of the HEMT at the fundamental frequency. The input reflector network is the same as the previous case ( $\ell_4 = \lambda_{2f_o}/2$  and  $\ell_3 = \lambda_{2f_o}/4$ ).

Two separate designs incorporated, respectively, one- and two-section filters for the bandpass structures. Fig. 8 shows the performance of the one-section design (6-dB conversion gain, greater harmonic suppression  $\geq 25$  dBc over a wider band due to filter action). The second (two-section) design (Fig. 9) provides 4.5-dB conversion gain and greatly improved harmonic suppression ( $\approx -50$  dBc).

Fig. 8. Narrow-band HEMT doubler design with one section filter.

Fig. 9. Narrow-band HEMT doubler design with two section filter.

Fig. 10. Medium-band HEMT doubler design.

### B. Wider Bandwidth Designs

Broader bandwidth HEMT multiplier conversion gain and harmonic suppression can be achieved by employing wider band reflector network responses. In particular, it is shown below that by extending the bandwidths of the output reflector network, significantly wider doubler frequency performance is achieved.

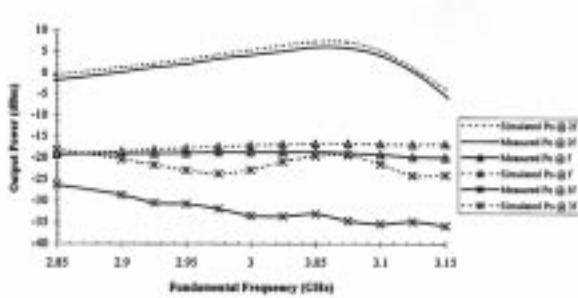

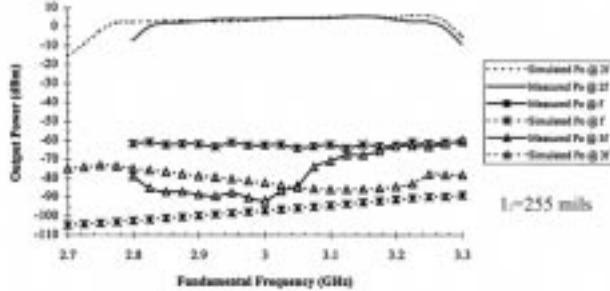

Synthesis of a medium-band HEMT multiplier realization is illustrated utilizing a HEMT/series transmission line for  $\ell_2$ /bandpass filter cascade. The output reflector network employs a 15% edge-coupled bandpass filter and the input reflector network is the nominal design discussed earlier ( $\ell_4 = \lambda_{2f_0}/2$  and  $\ell_3 = \lambda_{2f_0}/4$ ) As in previous designs, the cascaded transmission line provides the proper reflection phase angle of the fundamental frequency at the output. Fig. 10 is a plot of measured and modeled gain responses for second, fundamental, and third harmonic signals emerging from the HEMT multiplier. A perusal of this figure reveals doubler conversion gains of  $4 \text{ dB} \pm 1 \text{ dB}$  have been achieved with a 3-dB bandwidth of 15%. Furthermore, fundamental and third harmonic suppression is observed to be greater than 65 dBc.

Wider band designs are synthesized by extension of the concept utilized for medium-band responses. In this case, the filter employed in

Fig. 11. Wide-band HEMT doubler design.

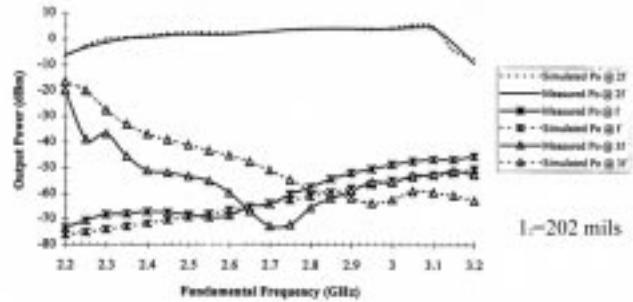

the output reflector cascade is a 45% fifth-order realization [7] and the input reflector is the nominal realization used previously. The measured and modeled responses in Fig. 11 demonstrate extended conversion gain bandwidth performance and excellent harmonic suppression. This figure demonstrates conversion gain of  $3 \text{ dB} \pm 1 \text{ dB}$ , 3-dB bandwidth of 35%, and fundamental and third harmonic frequency suppression of greater than 45 dBc.

### IV. CONCLUSION

This paper has presented techniques for synthesis of active single-ended frequency doublers employing HEMT transistors. These techniques incorporate reflector networks for providing excellent performance characteristics, which include efficient conversion gain and harmonic suppression. This performance is demonstrated quantitatively by both computer simulations and corresponding measured results. These results quantitatively illustrate the improvement in conversion gain using reflector networks on the input and output with proper phase angles to obtain optimum performance. These single-ended designs are useful for narrow- and wide-bandwidth applications. Since networks employing single stubs limit the operational bandwidth, incorporating filters into the designs provides bandwidth extension and improves the harmonic suppression. Of course, this improvement in bandwidth and harmonic suppression comes at the expense of the conversion gain. Another advantage of these designs is that they are single ended. This condition alleviates the necessity for complex baluns or transformers.

### REFERENCES

- [1] T. Hirota, "Uniplanar monolithic frequency doublers," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1249–1254, Aug. 1989.

- [2] M. Borg and G. R. Branner, "Novel MIC bipolar frequency doublers having high gain, wide bandwidth and good spectral performance," *IEEE Trans. Microwave Theory Tech.*, vol. 39, pp. 1936–1946, Dec. 1991.

- [3] C. Rauscher, "High-frequency doubler operation of GaAs field effect transistors," *IEEE Trans. Microwave Theory Tech.*, vol. 31, pp. 462–473, June 1983.

- [4] Y. Iyama *et al.*, "Second-harmonic reflector type high gain FET frequency doubler operating in  $K$ -band," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1989, pp. 1291–1294.

- [5] *EESOF Device Model Libraries*, vol. 10-10016, DL4.0A-011593, EESOF, Westlake Village, CA, 1993, pp. 8-1–8-2.

- [6] D. G. Thomas and G. R. Branner, "Optimization of active microwave frequency multiplier performance utilizing harmonic terminating impedances," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 2617–2624, Dec. 1996.

- [7] B. J. Minnis, "Printed circuit coupled line filters for bandwidths up to and greater than an octave," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-29, pp. 215–222, Mar. 1981.